- HOME >

- 専門家による技術解説 >

- まだまだ続く半導体微細化の最前線

まだまだ続く半導体微細化の最前線

2025.01.20

まだまだ続く半導体微細化の最前線

― 2nm世代を実現する3次元トランジスタとEUV露光の全体像 ―

1. 2nm時代の幕開け ― ラピダスと日本半導体復活への期待 ―

2024年12月に開催されたセミコン・ジャパン2024は盛況であった。ラピダスのためのセミコンと言った感じで、久々に日本の半導体業界が活気づいているとの印象であった。北海道千歳に建設中の前工程量産工場はほぼ完成し、12月中旬には最先端EUV露光装置が搬入される。これを皮切りに製造装置が次々に搬入されるという。IBMから技術移転を受けて、次世代2nmプロセスに対応するGAA(Gate-All-Around)トランジスタの量産を2027年に開始するという計画である。量産製造技術でトップを走るTSMCでは2025年から2nm技術を量産化する計画である。2年の遅れはあるにしろ、日本の現状を考えると、ラピダスの計画は意欲的である。日本が半導体技術で世界を席巻していた1990年頃を思い出す方も多いと思われる。

ところで、2nm技術は2nmの物理寸法を基準にしているのか?そんなに小さくて、トランジスタ動作するのか?2030年には1nm(10オングストローム)未満の技術が量産化される、などと言われると、当然疑問が湧いてくる。種を明かせば、2nmの物理寸法は使っていないが、3次元的デバイス構造によって、2nmと同じように集積密度を上げているという。この辺りの「からくり」をわかりやすく説明したいと考えている。

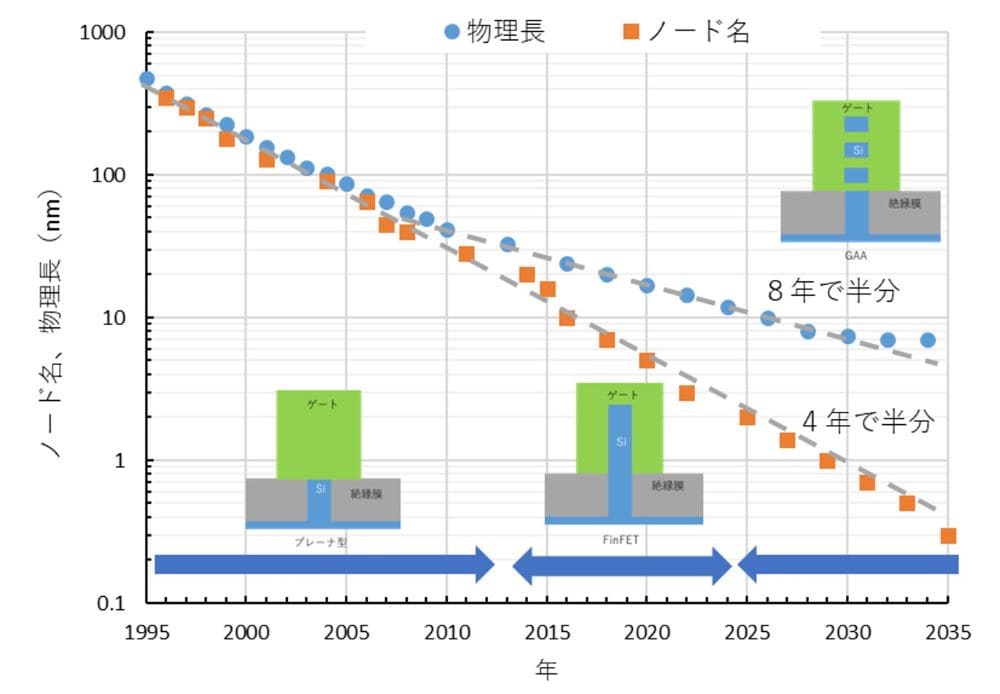

図. ロジック集積回路の微細化トレンド

2. 半導体微細化ロードマップの変遷

― ITRS/IRDSが示すロジックLSI進化の方向性 ―

1998年から国際半導体技術ロードマップ(ITRS: International Technology Roadmap for Semiconductors)を策定していたITRS委員会が、2016年に活動を終えた。その後は、IEEE傘下のIRDS(International Roadmap for Devices and Systems)が引き継いで、毎年ロードマップを策定している。微細化のトレンドについてもロードマップの中でまとめられている。

日本が世界を席巻していた当時、微細化を牽引していたのはメモリ(DRAM)であった。しかし、DRAMはトランジスタよりキャパシタが制限要因となって、高集積化が停滞している。現在の微細化を牽引しているのはMPU、GPUやDSPなどのロジックLSIである。飛ぶ鳥落とす勢いのNVIDIAのGPU、AIデータセンタで使われる大規模スイッチLSIや光通信用DSP、あるいはスマートフォン用APUも、争うように最先端の微細化技術を使用している。旺盛な生成AI絡みの需要から考えて、ロジックLSIに対する微細化の要求は当面継続すると考えるのが自然である。LSIの微細化技術の開発と量産工場の保有が国家の存亡にかかわるキー技術となり、各国はあからさまに補助金を投入している。ラピダスの計画もその一環であることは疑いの余地がない。

Mooreが集積回路当たりのトランジスタ搭載数は毎年2倍になるとのムーアの法則を提唱したのは今から60年前の1965年である。その後、2年で2倍になると修正されはしたものの、いまだに継続している。パターン寸法に換算すると4年で半分(集積度は4倍)に微細化されるということになる。業界の寡占化(最先端ロジックLSIではTSMC、IntelとSamsungの3社)も進み、ムーアの法則もそろそろ限界か、と言われているときに、この生成AIのムチが入った。知恵を出すよりほかはない。

図面は、ITRSやIRDSおよびTSMCのロードマップなどを参考に筆者が独自にまとめたロジックLSI量産技術の微細化のトレンドである。物理長(実寸法)と書いているものは、微細なパターンの代表例である配線メタルのハーフピッチ、あるいはゲート長との平均寸法である。ノード名とあるのは、TSMCなどが勝手に命名しているノード名の寸法である(例えば次世代2nmGAA技術の2nm)。2010年頃まで両者は良い一致を示していた。その後両者は乖離し始める。物理寸法は8年で半分と減速し、2030年頃には7nmで飽和すると予測されている。これに対してノード名の技術寸法は、4年で半分のムーアの法則を従っている。ほぼ2年ごとに新しい世代の技術が投入され、それに前世代の7割の寸法の数字を割り当てている(10nm→7nm→5nm→3nm→2nm)だけで、物理寸法とは何の関係もないとの意見もある。顧客を呼び込むためのマヤカシの看板に過ぎないのか?

さにあらず。エリアスケーリングを表しているという。つまり、世代ごとに面積当たりに集積化できるトランジスタの数量が約2倍になり、これを寸法に換算して世代ごとに0.7(1/√2)としている。実寸法を0.7倍にしなくても密度を2倍にできるのは、3次元構造のトランジスタを採用しているからである。図でも示されているように、実寸法と名目寸法(ノード名寸法)が乖離し始めたのは、プレーナ構造に替わり、フィンの側面と上面にゲートを形成する3次元トランジスタ構造が採用されたFinFETからである。有効面積が増え、より多くのトランジスタを集積化することでできる。そのトランジスタ密度の増分を等価的な寸法の縮小に換算したのがノード名寸法ということになる。なお、3次元トランジスタ構造については後ほど説明する。

3. 半導体微細化の鍵を握るEUV露光技術

微細化を実現する鍵となる技術が露光技術である。電子ビーム露光技術は研究には適しているが、量産には向かない。フォトマスクの作りやすさなどから、密着露光より縮小投影露光がよい。光露光の最小寸法は光の波長で規定されるため、短波長化が進められてきた。g線(436nm),i線(365nm),さらにエキシマレーザのKrF線(248nm),ArF線(193nm)と進んだ。純水の中では、屈折率(1.44)分だけ波長が短くなり、解像度は良くなる。例えば、ArFで空気中では解像度は65nm,液浸では45nmとなる。露光とエッチングを繰り返す、あるいは、側壁堆積膜を用いるマルチパターニングと呼ばれる手法を用いることで、解像度限界を超える微細なパターニングも可能である。例えば、ノード名寸法10nmのFinFETへの適用も可能である。

露光装置の延命技術としては有効であるが、マスク枚数が増え、工程が複雑になるとの欠点が目立つようになった。この状況をブレイクしたのが、波長13.5nmのEUV(極端紫外線)を用いる露光技術である。1パターン1回の露光で済むので、複雑な回路パターンが要求されるロジックLSIに採用され、ノード名10nm以下の微細化を支えることとなった。EUV技術の歴史は1996年まで遡る。開発には多くの時間とリソースがかかり、2017年に商用化されるも、提供できるのはオランダのASML社だけである。日本の大手ステッパメーカーのニコンとキャノンはEUV開発から撤退した。TSMCはいち早くEUN露光の量産導入に成功したが、Intelは時間がかかり、それが今日の両社の明暗を分けることとなった。ラピダスに導入されるのもこのEUV露光装置で、その立上げが急がれるところである。

4. 3次元トランジスタへの進化 ― FinFETからGAA・CFETへ ―

ロジックLSIを構成するトランジスタは金属-酸化膜-半導体電界効果トランジスタ(MOSFET)で、Si半導体表面の反転層チャネルのキャリア密度をゲート電圧による電界で制御する原理に基づいている。プレーナ型(2次元型)と呼ばれる構造は、図の構造図(電流に対して垂直方向の断面図)で示しているように、平坦な半導体表面を利用する。

これに対してFinFETと呼ばれる3次元型は、半導体表面に魚の背びれのようなフィン形状の加工をし、その上面だけでなく側面にも酸化膜-ゲート金属のゲート構造を形成する(構造図参照)。電流の流れる反転層チャネルはフィン側面にも形成される。有効面積を平面積以上に大きくすることができ、その分トランジスタの集積密度を上げることができる。

GAAトランジスタは、その名の示すように半導体チャネルの四面をゲートで覆った構造であり、さらに複数の半導体チャネル(ナノシート)を縦方向に積層する。反転層チャネルの面積が増えるのは言うまでもない。TSMCが2025年に量産導入する2nm技術に採用され、この構造をベースに微細化が進むと考えられている。

3次元化するのは半導体構造だけではない。配線構造は通常表面側に形成される。信号を伝送する微細なラインと、直流やグラウンドを供給する電源線がある。裏面電源供給BSPDN(Backside Power Delivery Network)技術は、電源線を裏面から供給する技術である。基板を薄くして、電源線を裏面からビアを介してソース/ドレインに接続する。大きな面積を占める電源線を裏面にすることで、必要面積を削減できるだけでなく、寄生容量や寄生抵抗が削減され、高速・低消費電力化にも大きな効果が期待できる。この技術は次々世代の1.6nm技術に適用される見込みである。

ロジックLSIはP型MOSFETとN型MOSFETを直列に接続し、ゲート電極を共通化したCMOS(相補型MOSFET)回路を基本とする。ON/OFFが変化する遷移時間以外は電流が流れないため、消費電力が小さいからである。GAAトランジスタは複数のチャネルが垂直方向に積層されているが、N型かP型のいずれかであり、CMOSを形成するには、平面方向に2つ並べる必要がある。これを垂直に積層するのがCFET(Complementary FET)と呼ばれる技術で、1nm技術辺りから採用される見込みである。横に並んでいたのを縦積みするわけであるから、同じ物理長(実寸法)で、集積密度を2倍にすることができる。

これ以外にも、絶縁膜の壁を挟んで左右にナノシートトランジスタを形成するフォークシート(Forksheet)FETなどの研究開発も行われている。

当面、実寸法の縮小は飽和気味であるが、3次元構造によるトランジスタの集積密度の向上(実効的な微細化)の歩みは止まりそうにない。

5. 3次元集積がもたらす高密度化の加速

かつては、NANDフラッシュメモリも微細化によって集積密度を向上させていた。2014年に15nm技術を適用して128Gbのプレーナ型のNANDプラッシュメモリが製品化されている。

しかし、2次元的集積化には限界があるため、3次元的に積層する構造へと舵を切ったのは2015年である。板状の電極と絶縁体を交互に積層し、垂直方向に複数の穴を開け、穴の内側に円筒状に電荷蓄積層、トンネル絶縁膜およびチャネル半導体を形成することで、多層のメモリを形成することができる。2015年に48層,2018年に96層,2020年に112層,2022年に162層,2024年には218層も積層して2Tbの高密度メモリを実現している。さらに、チップを薄層化して16段(チップ)積層することで、パッケージ当り4TBの大容量化を達成している。縦方向の積層集積化の勢いは止まらない。

先に見たように、ロジックLSIも3次元的な積層に進んでいくと思われる。その転機が2025年に導入されるGAAトランジスタ技術であると見られている。

これに対して、かつて微細化・高集積化を牽引したDRAMはやや停滞しているように見える。1990年代後半から、DRAM技術の方向性が高集積化から高速化に移ったのも、集積密度の向上が鈍化した理由と言われている。1トランジスタ1キャパシタの単純な構造であるが、キャパシタの占める体積が大きいことも集積化を阻害している。特に、3次元化を困難にしていると言える。

ところで、生成AIでパラメータ数が年率10倍以上で増えていることから、パラメータを蓄積するDRAMも極めて大きな容量の増大が求められている。メモリの壁などとAIの進展を阻害する壁の一つとも言われている。DRAMチップをTSV(Through Silicon Via)で3次元的に積層したHBMと呼ばれるメモリをGPUと同じパッケージ内に搭載している。現在12段までの積層化が実装技術で実現しているが、NANDフラッシュメモリ同様にモノリシックで集積化することが好ましい。いくつかの技術が検討されている。今後の3次元化の目玉となる技術領域であろう。

6. AI時代が牽引する半導体微細化の行方

水平方向のパターンの微細化の限界が見え始めたところにAIブームである。ロジック回路もメモリ回路も今まで以上のスピードでの集積密度の増大が要求されている。シーズ指向で技術開発が進み、その後キラーアプリケーションが出てくるといった技術の流れをよく見てきた。「誰が使うのか?」と言われながら、孤独に技術開発を進めてきたものである。半導体の微細化・高密度化は、これとは真逆のニーズ指向である。計算&メモリハングリーな生成AIが、凄い勢いで走り始めていてゴールは見えない。しかも国家レベルの競争になっている。まだまだ、鞭うたれながらの半導体微細化技術の開発が進められると思われる。日本にとっては20年以上の停滞からの突然の覚醒であり、これをチャンスと呼ばずして何と呼べばよいのか。

株式会社英知継承では、本テーマに関して当該専門家による技術コンサルティング(技術支援・技術調査)が可能です。下記よりお気軽にお問い合わせください。

▼「電気電子・光通信」に関連する技術解説一覧

Co-Packaged Optics(CPO)とフォトニック集積回路(PIC)

ダイヤモンド半導体はSiC・GaNを超えるか? 究極のパワー半導体材料

テラヘルツ通信を支えるTHz-over-Fiberの仕組みと応用

直流給電(DC給電)はZEHを加速するか? 住宅DC化の最新動向と課題

量子センサとは何か ― 原理・種類・応用から実用化動向まで ―

DRAMとSSDのギャップを埋める高速不揮発性メモリの最新動向

自動運転を支える車載E/Eアーキテクチャと車載ネットワークの最新動向